### **NPN/PNP Dual Silicon Transistors**

- Available in JAN, JANTX and JANTXV per MIL-PRF-19500/421

- Unitized, Dual Transistors

- Electrically Isolated, Complimentary NPN and PNP

- TO-78 and U package types

Rev. V1

## Electrical Characteristics (T<sub>A</sub> = +25°C unless otherwise specified)

| Parameter                              | Test Conditions                                                                                                                                                                                                                                                                                                                     | Symbol                                                                                                               | Units           | Min.                              | Max.     |

|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------------------|----------|

|                                        |                                                                                                                                                                                                                                                                                                                                     |                                                                                                                      |                 |                                   |          |

| Collector - Emitter Breakdown Voltage  | I <sub>c</sub> = 10 mA dc                                                                                                                                                                                                                                                                                                           | $V_{(BR)CEO}$                                                                                                        | V dc            | 40                                | _        |

| Collector - Base Cutoff Current        | $V_{CB}$ = 60 V dc<br>V <sub>CB</sub> = 50 V dc                                                                                                                                                                                                                                                                                     | I <sub>CBO1</sub><br>I <sub>CBO2</sub>                                                                               | µA dc<br>nA dc  | _                                 | 10<br>10 |

| Emitter - Base Cutoff Current          | $V_{EB}$ = 5.0 V dc<br>V <sub>EB</sub> = 3.0 V dc                                                                                                                                                                                                                                                                                   | I <sub>EBO1</sub><br>I <sub>EBO2</sub>                                                                               | µA dc<br>nA dc  | _                                 | 10<br>10 |

|                                        |                                                                                                                                                                                                                                                                                                                                     |                                                                                                                      |                 |                                   | Г.       |

| Forward Current Transfer Ratio         | $V_{CE} = 1.0 \text{ V dc}; I_{C} = 150 \text{ mA dc}$ $V_{CE} = 10 \text{ V dc}; I_{C} = 100 \text{ µA dc}$ $V_{CE} = 10 \text{ V dc}; I_{C} = 1.0 \text{ mA dc}$ $V_{CE} = 10 \text{ V dc}; I_{C} = 10 \text{ mA dc}$ $V_{CE} = 10 \text{ V dc}; I_{C} = 150 \text{ mA dc}$ $V_{CE} = 10 \text{ V dc}; I_{C} = 300 \text{ mA dc}$ | h <sub>FE1</sub><br>h <sub>FE2</sub><br>h <sub>FE3</sub><br>h <sub>FE4</sub><br>h <sub>FE5</sub><br>h <sub>FE6</sub> | h <sub>FE</sub> | 50<br>35<br>50<br>75<br>100<br>35 | 300      |

| Collector - Emitter Saturation Voltage | $I_{B}$ = 15 mA dc; $I_{C}$ = 150 mA dc                                                                                                                                                                                                                                                                                             | V <sub>CE(SAT)</sub>                                                                                                 | Vdc             | _                                 | 0.40     |

| Base - Emitter Saturation Voltage      | $I_B$ = 15 mA dc; $I_C$ = 150 mA dc                                                                                                                                                                                                                                                                                                 | V <sub>BE(SAT)</sub>                                                                                                 | Vdc             | 0.8                               | 1.25     |

|                                        |                                                                                                                                                                                                                                                                                                                                     | V BE(SAT)                                                                                                            | Vuc             | 0.0                               | 1.2      |

VPT Components and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit <u>www.vptcomponents.com</u> for additional data sheets and product information.

## **NPN/PNP Dual Silicon Transistors**

Rev. V1

## Electrical Characteristics ( $T_A = +25^{\circ}C$ unless otherwise specified)

| Parameter                                                                    | Test Conditions                                                               | Symbol                             | Units | Min. | Max. |

|------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------|-------|------|------|

| Small-Signal Short-Circuit Forward<br>Current Transfer Ratio                 | V <sub>CE</sub> = 10 V dc; I <sub>C</sub> = 1 mA dc; f = 1 kHz                | h <sub>fe</sub>                    | _     | 60   | 300  |

| Small-Signal Common Emitter Input<br>Impedance                               | V <sub>CE</sub> = 10 V dc; I <sub>C</sub> = 1 mA dc; f = 1 kHz                | h <sub>ie</sub>                    | kΩ    | 1.5  | 9    |

| Small-Signal Common Emitter Output<br>Admittance                             | V <sub>CE</sub> = 10 V dc; I <sub>C</sub> = 1 mA dc; f = 1 kHz                | h <sub>oe</sub>                    | µhmo  | _    | 50   |

| Collector-Base Cutoff Current                                                | $T_{A} = +150^{\circ}C$ $V_{CB} = 50 \text{ V dc}$                            | I <sub>CBO3</sub>                  | µA dc | _    | 10   |

| Forward Current Transfer Ratio                                               | $T_{A} = -55^{\circ}C$ $V_{CE} = 10 \text{ V dc; } I_{C} = 10 \text{ mA dc}$  | h <sub>FE7</sub>                   | _     | 12   | _    |

|                                                                              |                                                                               |                                    |       |      |      |

| Magnitude of<br>Small-Signal Short-Circuit<br>Forward Current Transfer Ratio | V <sub>CE</sub> = 10 V dc; I <sub>C</sub> = 20 mA dc; f = 100 MHz             | h <sub>fe</sub>                    | _     | 2.0  | 10   |

| Open Circuit Output Capacitance                                              | V <sub>CB</sub> = 10 V dc; I <sub>E</sub> = 0; 100 kHz ≤ f ≤ 1 MHz            | C <sub>obo</sub>                   | pF    |      | 8.0  |

| Noise Figure                                                                 | $V_{CE}$ = 10 V dc; $I_{C}$ = 100 $\mu A$ dc; f = 1kHz; $R_{G}$ = 1 $k\Omega$ | NF                                 | _     | 8    | dB   |

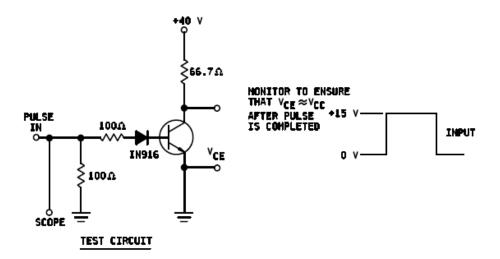

| Collector Emitter Nonlatching Voltage                                        | See figure 10                                                                 | V <sub>CE</sub>                    | V dc  | 40   | _    |

| Switching Characteristics                                                    |                                                                               |                                    |       |      |      |

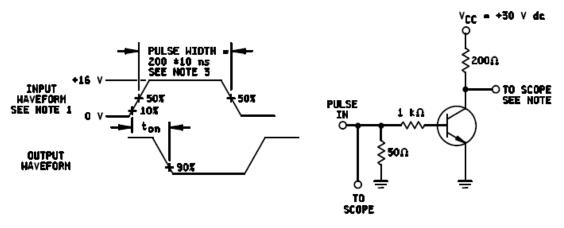

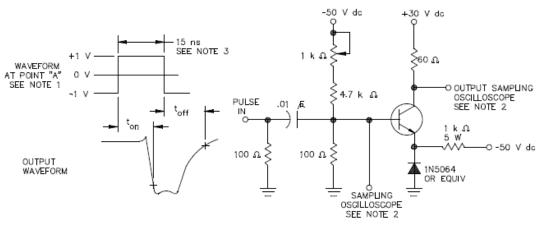

| Turn-On Time (saturated)                                                     | See figure 7                                                                  | t <sub>on</sub>                    | ns    | _    | 45   |

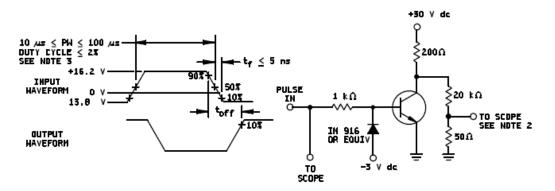

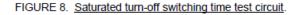

| Turn-Off Time (saturated)                                                    | See figure 8                                                                  | t <sub>off</sub>                   | ns    | _    | 300  |

| Pulse Response                                                               | See figure 9                                                                  | t <sub>on</sub> + t <sub>off</sub> | ns    |      | 18   |

<sup>2</sup>

VPT Components and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit <u>www.vptcomponents.com</u> for additional data sheets and product information.

## NPN/PNP Dual Silicon Transistors

Rev. V1

## Absolute Maximum Ratings ( $T_A = +25^{\circ}C$ unless otherwise specified)

| Ratings                                                                               | Symbol             | Value                                          |

|---------------------------------------------------------------------------------------|--------------------|------------------------------------------------|

| Collector - Emitter Voltage                                                           | V <sub>CEO</sub>   | 40 V dc                                        |

| Collector - Base Voltage                                                              | V <sub>CBO</sub>   | 60 V dc                                        |

| Emitter - Base Voltage                                                                | V <sub>EBO</sub>   | 5.0 V dc                                       |

| Collector Current                                                                     | Ι <sub>C</sub>     | 600 mA dc                                      |

| Total Power Dissipation<br>@ T <sub>A</sub> = +25°C<br>One Transistor<br>Total Device | PT                 | 0.30 W <sup>(4)</sup><br>0.60 W <sup>(4)</sup> |

| Total Power Dissipation<br>@ T <sub>C</sub> = +25°C<br>One Transistor<br>Total Device | P <sub>T</sub> (1) | 1.0 W <sup>(5)</sup><br>2.0 W <sup>(5)</sup>   |

| Operating & Storage Temperature Range                                                 | $T_{J},T_{STG}$    | -65°C to +200°C                                |

| V <sub>1C—2C</sub>                                                                    | V dc               | <u>+</u> 120                                   |

| Lead To Case Voltage                                                                  | V dc               | <u>+</u> 120                                   |

#### **Thermal Characteristics**

| Types   | R₀ <sub>JA</sub> | R₀ <sub>JA</sub> | R <sub>∗JSP</sub>  | R <sub>∘JSP</sub> |

|---------|------------------|------------------|--------------------|-------------------|

|         | One Transistor   | Total Device     | One Section        | Both Sections     |

| 2N4854  | <u>°C/W</u>      | <u>°C/W</u>      | <u>°C/W</u>        | <u>°C/W</u>       |

| 2N4854U | 350              | 290              | 110 <sup>(6)</sup> | 90 <sup>(6)</sup> |

(1)  $T_C$  rating does not apply to surface mount devices (2N4854U).

(2) For  $T_A > +25^{\circ}C$ , derate linearly 1.43 mW/°C one transistor, 2.00 mW/°C both transistors. (3) For  $T_C > +25^{\circ}C$ , derate linearly 4.0 mW/°C one transistor, 8.0 mW/°C both transistors.

(4) For  $T_A > +25^{\circ}$ C, derate linearly 1.71 mW/°C one transistor, 3.43 mW/°C both transistors

(5) For  $T_c > +25^{\circ}$ C, derate linearly 5.71 mW/°C one transistor, 11.43 mW/°C both transistors.

(6) For U package the thermal resistance is  $R_{eSP}$ .

VPT Components and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.vptcomponents.com for additional data sheets and product information.

NPN/PNP Dual Silicon Transistors

Rev. V1

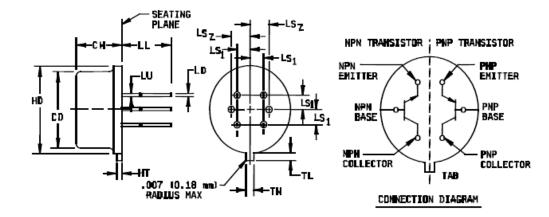

Outline Drawing (TO-78)

|     | Dimensions |       |             |       |       |

|-----|------------|-------|-------------|-------|-------|

| Ltr | Inches     |       | Millimeters |       | Notes |

|     | Min        | Max   | Min         | Max   |       |

| CD  | .305       | .335  | 7.75        | 8.51  |       |

| CH  | .140       | .260  | 3.56        | 6.60  |       |

| HD  | .335       | .370  | 8.51        | 9.40  |       |

| HT  | .009       | .125  | 0.23        | 3.18  |       |

| LD  | .016       | .021  | 0.41        | 0.53  | 3, 7  |

| LL  | .500       | 1.750 | 12.70       | 44.45 | 7     |

| Dimensions |                       |      |            |      |      |

|------------|-----------------------|------|------------|------|------|

| Ltr        | Inches Millimeters    |      | Notes      |      |      |

|            | Min                   | Max  | Min        | Max  |      |

| LS1        | .0707 Nom. 1.796 Nom. |      | 5          |      |      |

| LS2        | .1000                 | Nom. | 2.540 Nom. |      | 5    |

| LU         | .016                  | .019 | 0.41       | 0.48 | 4, 7 |

| TL         | .029                  | .045 | 0.74       | 1.14 | 6    |

| TW         | .028                  | .034 | 0.71       | 0.86 |      |

NOTES:

- 1. Dimensions are in inches.

- 2. Millimeters are given for general information only.

- 3. Measured in the zone beyond .250 inch (6.35 mm) from the seating plane.

- 4. Measured in the zone .050 inch (1.27 mm) and .250 inch (6.35 mm) from the seating plane.

- 5. When measured in a gauging plane .054 +.001, -.000 inch (1.37 +0.03, -0.00 mm) below the seating plane of the transistor, maximum diameter leads shall be within .007 inch (0.18 mm) of their true location relative to a maximum width tab. Smaller diameter leads shall fall within the outline of the maximum diameter lead tolerance.

- 6. Measured from the maximum diameter of the actual device.

- 7. All six leads.

- 8. In accordance with ASME Y14.5M, diameters are equivalent to \$\phix\$ symbology.

FIGURE 2. Physical dimensions of transistor type 2N4854 (all guality levels, similar to TO-78).

VPT Components and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.vptcomponents.com for additional data sheets and product information.

### **NPN/PNP Dual Silicon Transistors**

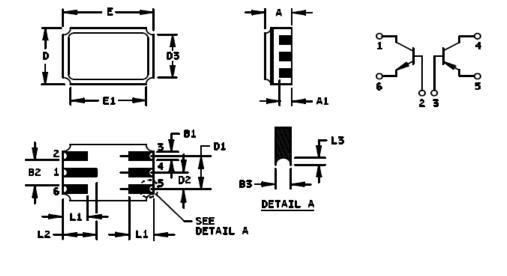

### **Outline Drawing (U)**

| Ltr            | Dimensions |      |        |        |

|----------------|------------|------|--------|--------|

|                | Inches     |      | Millin | neters |

|                | Min        | Max  | Min    | Max    |

| Α              | .058       | .100 | 1.47   | 2.54   |

| A1             | .026       | .039 | 0.66   | 0.99   |

| B <sub>1</sub> | .022       | .028 | 0.56   | 0.71   |

| B <sub>2</sub> | .072       | Ref. | 1.83   | Ref.   |

| B <sub>3</sub> | .006       | .022 | 0.15   | 0.56   |

| D              | .165       | .175 | 4.19   | 4.45   |

| D1             | .095       | .105 | 2.41   | 2.67   |

| Ltr            | Dimensions |        |      |        |  |

|----------------|------------|--------|------|--------|--|

|                | Inc        | Inches |      | neters |  |

|                | Min        | Max    | Min  | Max    |  |

| D <sub>2</sub> | .045       | .055   | 1.14 | 1.40   |  |

| Dз             |            | .175   |      | 4.45   |  |

| E              | .240       | .250   | 6.10 | 6.35   |  |

| E1             |            | .250   |      | 6.35   |  |

| L <sub>1</sub> | .060       | .070   | 1.52 | 1.78   |  |

| L <sub>2</sub> | .082       | .098   | 2.08 | 2.49   |  |

| L3             | .003       | .007   | 0.08 | 0.18   |  |

#### NOTES:

Dimensions are in inches.

2. Millimeters are given for general information only.

The coplanarity deviation of all terminal contact points, as defined by the device seating plane, shall not exceed .006 inch (0.15 mm) for solder dipped leadless chip carriers.

FIGURE 3. Physical dimensions of transistor type 2N4854U.

VPT Components and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit <u>www.vptcomponents.com</u> for additional data sheets and product information.

Rev. V1

### **NPN/PNP Dual Silicon Transistors**

Rev. V1

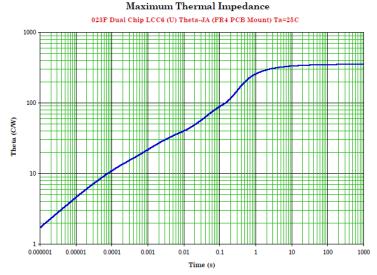

#### Graphs

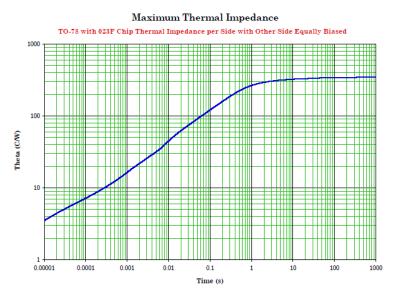

Thermal resistance =  $350^{\circ}$ C/W one side,  $290^{\circ}$ C/W both sides operating in "parallel". Ta =  $25^{\circ}$ C (PCB FR4 Mounted).

FIGURE 5. Thermal impedance graph (ReJPCB) for 2N4854U (U).

Thermal impedance TO-78 package dual 023F chips, Thermal resistance =  $350^{\circ}$ C/W one side, 290°C/W both sides operating in "parallel". T<sub>A</sub> =  $25^{\circ}$ C (air cooled).

FIGURE 6. Thermal impedance graph (ReJA) for 2N4854 (all quality levels, similar to TO-78).

VPT Components and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit <u>www.vptcomponents.com</u> for additional data sheets and product information.

### **NPN/PNP Dual Silicon Transistors**

Rev. V1

### **Test Circuits**

#### NOTES:

- The rise time (t<sub>2</sub>) of the applied pulse shall be ≤ 2.0 ns, duty cycle ≤ 2 percent, and the generator source impedance shall be 50 Ω.

- Sampling oscilloscope: Z<sub>IN</sub> ≥ 100 kΩ, C<sub>IN</sub> ≤ 12 pF, rise time ≤ 0.2 ns.

- The signs, polarity symbols, and waveforms shown are for the NPN transistor; the signs and polarity symbols are reversed for the PNP triode (see 1.2 herein).

FIGURE 7. Saturated turn-on switching time test circuit.

#### NOTES:

- The rise time (t<sub>r</sub>) of the applied pulse shall be ≤ 2.0 ns, duty cycle ≤ 2 percent, and the generator source impedance shall be 50 Ω.

- 2. Sampling oscilloscope:  $Z_{IN} \ge 100 \text{ k}\Omega$ ,  $C_{IN} \le 12 \text{ pF}$ , rise time  $\le 0.2 \text{ ns}$ .

- The signs, polarity symbols, and waveforms shown are for the NPN transistor; the signs and polarity symbols are reversed for the PNP triode (see 1.2 herein).

VPT Components and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit <u>www.vptcomponents.com</u> for additional data sheets and product information.

## NPN/PNP Dual Silicon Transistors

Rev. V1

### **Test Circuits**

#### NOTES:

- The rise time (t<sub>r</sub>) of the applied pulse shall be ≤ 2.0 ns, duty cycle ≤ 2 percent, and the generator source impedance shall be 50 Ω.

- 2. Sampling oscilloscope:  $Z_{IN} \ge 100 \text{ k}\Omega$ ,  $C_{IN} \le 12 \text{ pF}$ , rise time  $\le 0.2 \text{ ns}$ .

- The signs, polarity symbols, and waveforms shown are for the NPN transistor; the signs and polarity symbols are reversed for the PNP triode (see 1.2 herein).

FIGURE 9. Nonsaturated switching time test circuit.

FIGURE 10. Collector emitter nonlatching voltage test circuit.

8

VPT Components and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit <u>www.vptcomponents.com</u> for additional data sheets and product information.

**NPN/PNP Dual Silicon Transistors**

#### VPT COMPONENTS. ALL RIGHTS RESERVED.

Information in this document is provided in connection with VPT Components products. These materials are provided by VPT Components as a service to its customers and may be used for informational purposes only. Except as provided in VPT Components Terms and Conditions of Sale for such products or in any separate agreement related to this document, VPT Components assumes no liability whatsoever. VPT Components assumes no responsibility for errors or omissions in these materials. VPT Components may make changes to specifications and product descriptions at any time, without notice. VPT Components makes no commitment to update the information and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to its specifications and product descriptions. No license, express or implied, by estoppels or otherwise, to any intellectual property rights is granted by this document.

THESE MATERIALS ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, RELATING TO SALE AND/OR USE OF VPT COMPONENTS PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, CONSEQUENTIAL OR INCIDENTAL DAMAGES, MERCHANTABILITY, OR INFRINGEMENT OF ANY PA-TENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. VPT COMPONENTS FURTHER DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CON-TAINED WITHIN THESE MATERIALS. VPT COMPONENTS SHALL NOT BE LIABLE FOR ANY SPECIAL, IN-DIRECT, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVE-NUES OR LOST PROFITS, WHICH MAY RESULT FROM THE USE OF THESE MATERIALS.

VPT Components products are not intended for use in medical, lifesaving or life sustaining applications. VPT Components customers using or selling VPT Components products for use in such applications do so at their own risk and agree to fully indemnify VPT Components for any damages resulting from such improper use or sale.

<sup>9</sup>

VPT Components and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit <u>www.vptcomponents.com</u> for additional data sheets and product information.